Mikroprocesorinių sistemų paskirtis. Įvadas: mikroprocesoriai, mikroprocesorinės sistemos Mikroprocesorinės sistemos sudėtis

Iš daugybės ir įvairių mikroprocesorių (MP) ir mikrokompiuterių taikymo sričių vieną pirmųjų vietų pagal apimtį ir panaudojimą užima mikroprocesorinės sistemos – objektinės skaičiavimo sistemos, pavyzdžiui, skirtos valdymui, diagnostikai, skaitmeninių signalų apdorojimui. ir vaizdai.

Mikroprocesorinėse sistemose tokia svarbi mikroprocesorių savybė kaip įterptumas– gebėjimas priartinti kompiuterines technologijas prie matavimo, valdymo, informacijos apdorojimo ar diagnostikos objekto.

Pagrindinės užduotys, kurias galima išspręsti naudojant mikroprocesorines sistemas, yra šios:

– sudėtingo technologinio proceso ar techninio objekto valdymas pagal nurodytus algoritmus;

– skaitmeninis signalo apdorojimas tiesiogiai signalo šaltinio vietoje;

– vaizdo apdorojimas – filtravimas, ryškinimas, kontūravimas, mastelio keitimas ir kt. techninėse regėjimo sistemose pramoniniuose robotuose, radarų sistemose, stebėjimo sistemose, navigacijoje ir kt.

– automatinių matavimo, valdymo, prognozavimo sistemų pritaikymas besikeičiančioms sąlygoms;

– lanksčių derinamų valdymo sistemų, skaitmeninių signalų ir vaizdo apdorojimo kūrimas;

– informacijos kaupimas ir išankstinis apdorojimas;

– daugiafunkcinių įrenginių kūrimas, esamų įrenginių galimybių išplėtimas;

– „protingų“ įrenginių ir sistemų kūrimas, didinant esamų įrenginių ir prietaisų intelekto lygį;

– savidiagnostikos ir įrangos testavimo įgyvendinimas.

Galimybė šias funkcijas diegti mikroprocesorinėse sistemose, kartu su elektronikos ir ryšių pasiekimais, matematinių matavimų signalų apdorojimo metodų kūrimu ir atitinkamos programinės įrangos sukūrimu sudarė būtinas prielaidas naujų kartų mikroprocesorinėms sistemoms atsirasti. ir įranga su šiomis galimybėmis:

- pilnas visų tipų informacijos apdorojimo automatizavimas, visų sistemos teikiamų funkcijų integravimas ir koordinavimas;

- sistemos sudėties didinimas ir jos funkcijų išplėtimas dėl magistralinės modulinės konstrukcijos ir programinės įrangos kūrimo struktūros;

– įvairūs algoritmai ir matavimo metodai;

- atliekamų užduočių decentralizavimas pagal funkcinius, organizacinius ir teritorinius požymius, dirbtinio intelekto įrankių prieinamumą, galimybę išmokti sistemą, jos pritaikymą ir optimizavimą;

– didelis patikimumas ir funkcinis patikimumas dėl savidiagnostikos ir testavimo priemonių bei sistemos valdymo lankstumo;

– galimybė susieti su kitomis skaičiavimo sistemomis.

Praktiniam aukščiau išvardintų užduočių įgyvendinimui reikia visapusiškai išspręsti mokslinius, techninius ir technologinius klausimus, susijusius su aparatinės ir programinės įrangos kūrimu ir plėtra, sudėtingų procesų ir techninių objektų matematinio modeliavimo metodais, analoginiu-skaitmeniniu ir skaitmeniniu-skaitmeniniu būdu. analoginiai keitikliai (DAC), sąsaja LSI ir kiti elektroniniai komponentai , naudojant šiuolaikines ryšio priemones ir, galiausiai, mokant darbuotojus, gebančius kompetentingai išspręsti nustatytas užduotis.

MP-sistemų konstravimo principai.

Bet kurios mikroprocesorinės sistemos šerdis yra mikroprocesorius arba tiesiog procesorius (iš anglų kalbos procesorius). Teisingiausia šį žodį išversti į rusų kalbą kaip „procesorių“, nes būtent mikroprocesorius yra mazgas, blokas, kuris atlieka visą informacijos apdorojimą mikroprocesoriaus sistemoje.

mikroprocesorius vadinsime programa valdomą įrenginį, skirtą apdoroti skaitmeninę informaciją ir generuoti šį apdorojimą valdančius signalus.

Likę mazgai atlieka tik pagalbines funkcijas: saugo informaciją (įskaitant valdymo informaciją, tai yra programas), bendrauja su išoriniais įrenginiais, bendrauja su vartotoju ir kt. Procesorius pakeičia praktiškai visą „kietą logiką“, kurios prireiktų tradicinėje skaitmeninėje sistemoje. Atlieka aritmetines funkcijas (sudėti, daugyba ir kt.), logines funkcijas (slinkimas, lyginimas, kodų maskavimas ir kt.), laikiną kodų saugojimą (vidiniuose registruose), kodų perkėlimą tarp mikroprocesorinės sistemos mazgų ir daug daugiau. Tokių elementarių procesoriaus atliekamų operacijų skaičius gali siekti kelis šimtus. Procesorių galima palyginti su sistemos smegenimis. Tačiau tuo pat metu reikia turėti omenyje, kad procesorius atlieka visas savo operacijas paeiliui, tai yra vienas po kito, savo ruožtu. Žinoma, yra procesorių Su lygiagrečiai vykdant kai kurias operacijas, yra ir mikroprocesorių sistemų, kuriose keli procesoriai lygiagrečiai atlieka tą pačią užduotį, tačiau tai retos išimtys. Viena vertus, nuoseklus operacijų vykdymas yra neabejotinas pranašumas, nes leidžia naudojant tik vieną procesorių atlikti bet kokius sudėtingiausius informacijos apdorojimo algoritmus. Tačiau, kita vertus, nuoseklus operacijų vykdymas lemia tai, kad algoritmo vykdymo laikas priklauso nuo jo sudėtingumo. Paprasti algoritmai veikia greičiau nei sudėtingi. Tai yra, mikroprocesorinė sistema sugeba viską, bet neveikia per greitai, nes visi informacijos srautai turi būti perduodami per vieną mazgą – mikroprocesorių (1.3 pav.). Tradicinėje skaitmeninėje sistemoje nesunku organizuoti lygiagretų visų informacijos srautų apdorojimą, tačiau tai gali apsunkinti grandinę.

vadovas

informacija

(programa)

Ryžiai. 1.3. Informacija teka mikroprocesorinėje sistemoje.

Taigi, mikroprocesorius gali atlikti daugybę operacijų. Tačiau kaip jis žino, kokią operaciją jam reikia atlikti šiuo metu? Tai yra nulemta valdymo informacija, programa.

Programa yra komandų (instrukcijų) rinkinys tai yra skaitmeniniai kodai, kuriuos iššifravęs, procesorius žinos, ką jam reikia daryti. Programą nuo pradžios iki galo sukompiliuoja žmogus, programuotojas, o procesorius veikia kaip paklusnus šios programos vykdytojas, nerodo jokios iniciatyvos (nebent, žinoma, yra tvarkingas). Todėl lyginti procesorių su smegenimis nėra labai teisinga. Jis yra tik algoritmo, kurį žmogus jam iš anksto sudarė, vykdytojas. Bet kokį nukrypimą nuo šio algoritmo gali sukelti tik procesoriaus ar kai kurių kitų mikroprocesorinės sistemos komponentų gedimas.

Visos procesoriaus vykdomos instrukcijos sudaro komandų procesoriaus sistemą. Procesoriaus instrukcijų rinkinio struktūra ir apimtis lemia jo greitį, lankstumą ir naudojimo paprastumą. Iš viso procesorius gali turėti nuo kelių dešimčių iki kelių šimtų instrukcijų. Instrukcijų sistema gali būti skirta siauram sprendžiamų užduočių spektrui (specializuotiems procesoriams) arba kuo platesniam užduočių spektrui (bendros paskirties procesoriams). Komandų kodai gali turėti skirtingą skaičių skaitmenų (užimti nuo vieno iki kelių baitų). Kiekviena komanda turi savo vykdymo laiką, todėl visos programos vykdymo laikas priklauso ne tik nuo komandų skaičiaus programoje, bet ir nuo to, kokios komandos yra naudojamos.

Instrukcijoms vykdyti procesoriaus struktūroje yra vidiniai registrai, aritmetinis loginis blokas (ALU, ALU – aritmetinis loginis vienetas), multiplekseriai, buferiai, registrai ir kiti mazgai. Visų mazgų veikimas sinchronizuojamas bendru išoriniu procesoriaus laikrodžio signalu. Tai yra, procesorius yra gana sudėtingas skaitmeninis įrenginys (1.4 pav.).

Ryžiai. 1.4. Paprasčiausio procesoriaus sandaros pavyzdys.

Tačiau mikroprocesorinių sistemų kūrėjui informacija apie vidinės procesoriaus struktūros subtilybes nėra labai svarbi. Kūrėjas procesorių turi vertinti kaip „juodąją dėžę“, kuri, reaguodama į įvesties ir valdymo kodus, atlieka vienokias ar kitokias operacijas ir gamina išėjimo signalus.

Kūrėjas turi žinoti komandų sistemą, procesoriaus darbo režimus, taip pat procesoriaus sąveikos su išoriniu pasauliu taisykles arba, kaip jie dar vadinami, informacijos mainų protokolus. .

Apie vidinę procesoriaus struktūrą reikia žinoti tik tai, kas būtina norint pasirinkti vieną ar kitą instrukciją, vieną ar kitą darbo režimą.

Mikroprocesorinė sistema - tai skaičiavimo, valdymo ir matavimo arba valdymo sistema, kurioje pagrindinis informacijos apdorojimo įrenginys yra MP. Mikroprocesorių sistema yra sukurta iš mikroprocesorių LSI rinkinio.

MPS sistemų konstravimas grindžiamas trimis principais: stuburas; moduliškumas; mikroprogramų valdymas.

Bagažinės principas nustato jungčių tarp MPS funkcinių blokų pobūdį – visi blokai sujungti į vieną sistemos magistralę.

Moduliškumo principas yra ta, kad sistema sukurta remiantis ribotu skaičiumi struktūriškai ir funkciškai užbaigtų modulių tipų. Kiekvienas MPS sistemos modulis turi trečią (didelės varžos) būsenos valdymo įvestį. Šis įrašas vadinamas СS (Сhір Select) – krištolo pasirinkimas arba OE (Output Enabie) – leidimas išeiti.

CS signalo veiksmas trigeriui parodytas fig. 1.5. Pradinis paleidimo signalas K bus rodomas išvestyje tik tada, kai aktyvus (įšiuo atveju – nulis) signalo lygis CS. Jei CS = 1, apverstas yra didelės varžos būsenoje. Trigerio išvestis yra trijų stabilių, tai yra, ji gali būti vienoje iš trijų būsenų: loginė viena, loginė nulis arba didelė varža. Kiekvienu laiko momentu prie MPS sistemos magistralės prijungiami tik du moduliai – tas, kuris priima informaciją, ir tas, kuris perduoda informaciją. Kiti yra didelės varžos būsenoje.

Stuburo ir moduliškumo principai leidžia padidinti MP valdymo ir skaičiavimo galimybes pridedant kitus modulius.

Firmware valdymo principas susideda iš galimybės atlikti elementarias operacijas - mikroinstrukcijas (pamainą, informacijos perdavimą, logines operacijas). Su tam tikru mikroinstrukcijų deriniu galite sukurti komandų rinkinį, kuris geriausiai atitiks sistemos paskirtį, tai yra sukurti technologinę kalbą.

Apsvarstykite apibendrintą MPS blokinę schemą (1.6 pav.) MPS sudaro: centrinis procesorius (CPU), PZP, OZP; pertraukimo sistema, laikmatis, UVV. Įvesties/išvesties įrenginiai prie sistemos magistralės prijungiami per I/O sąsajas.

Tik skaitymo atmintis ir laisvosios kreipties atmintis sudaro atminties sistemą, skirtą informacijai saugoti dvejetainių skaičių forma. Tik skaitymo atmintis skirta programoms, lentelėms, konstantoms saugoti.

Laisvosios kreipties atmintis – tarpiniams skaičiavimų rezultatams saugoti. Atmintis yra organizuota kaip langelių masyvas, kurių kiekvienas turi savo adresą ir turi baitą arba žodį.

CPU modulis apdoroja duomenis ir valdo visus kitus sistemos modulius. Centriniame procesoriuje, be LSI MP, yra sinchronizavimo grandinės ir sąsaja su sistemos magistrale. Jis paima komandų kodus iš atminties, juos iššifruoja ir vykdo. Vykdydamas komandą – komandų ciklą – CPU atlieka šiuos veiksmus:

Nustato instrukcijos adresą adresų magistralėje AB;

Gauna komandos kodą iš atminties ir jį iššifruoja;

Skaičiuoja operandų adresus ir nuskaito duomenis;

Atlieka komanda nurodytą operaciją;

Priima išorinius valdymo signalus (pavyzdžiui, pertraukimo užklausą);

Generuoja būsenos ir valdymo signalus, reikalingus atminties veikimui

ir UVV.

Įvesties / išvesties įrenginiai arba išoriniai įrenginiai yra įrenginiai, skirti įvesti informaciją į MP arba iš jo išvesti informaciją. ICD pavyzdžiai yra ekranai, spausdintuvai, klaviatūros, skaitmeninio į analoginį ir analoginį skaitmeninį keitikliai, relės ir jungikliai. Norint prijungti oro pūtiklius prie sistemos magistralės, jų signalai turi atitikti tam tikrus standartus. Tai pasiekiama naudojant I/O sąsajas.

Įvesties-išvesties sąsajos atlieka oro srauto signalų suderinimo su MP sistemos magistralės signalais funkciją. Jie taip pat vadinami valdikliais arba adapteriais. Mikroprocesorius prie sąsajų prisijungia naudodamas specialias I/O komandas. Tuo pat metu parlamentaras į autobusą įdeda adresus AB sąsajos adresą ir duomenų magistralėje DB nuskaito duomenis iš įvesties įrenginio arba rašo į išvesties įrenginį. Ant pav. 1.6 rodo vieną įvesties sąsają ir vieną išvesties sąsają.

Pertraukimo sistema leidžia MPS reaguoti į išorinius signalus – pertraukimo užklausas, kurių šaltiniai gali būti: parengties signalai iš išorinių įrenginių, signalai iš generatorių, signalai iš jutiklių išėjimų. Kai atsiranda pertraukimo užklausa, centrinis procesorius pertraukia pagrindinę programą ir pradeda vykdyti pertraukimo užklausos paslaugos tvarką. Norint sukurti pertraukimo sistemą, MPC yra specialių programuojamų pertraukimų valdiklių LSI.

Laikmatis skirtas funkcijoms, susijusioms su laiko nustatymu, įgyvendinti. MP įkeliant į laikmatį skaičių, nurodantį dažnį, delsą arba padalijimo koeficientą, laikmatis pats įgyvendina norimą funkciją.

Parengė Sergejus

Magnitogorsko valstybinė profesinė pedagoginė kolegija

Magnitogorskas, 2005 m

1. Mikroprocesorinės sistemos loginė struktūra

Projektuojant stebėjimo, valdymo ar skaičiavimo sistemas mikroprocesoriaus pagrindu, būtina išsiaiškinti ir aprašyti sistemoje atliekamas funkcijas, o vėliau jas derinti su tų mikroprocesorių galimybėmis, kurios gali būti naudojamos projektuojamoje sistemoje.

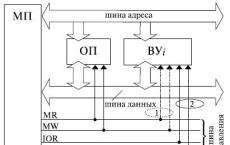

Tikroje elektroninėje sistemoje, pagrįstoje mikroprocesoriumi, yra daug funkcinių įrenginių, iš kurių vienas yra mikroprocesorius. Visi sistemos įrenginiai turi standartinę sąsają ir yra prijungti prie vienos informacijos magistralės, kaip parodyta 1 pav.

Mikroprocesorius, priklausomai nuo sistemos reikalavimų, gali būti vieno lusto arba vienos plokštės įrenginys, sukurtas kelių mikroprocesorių LSI rinkinio pagrindu. Didelio našumo sistemose mikroprocesorius yra sukurtas remiantis dvipoliais LSI mikroprocesoriaus sekcijomis.

Mikroprocesorius sistemoje atlieka centrinio valdymo bloko ir aritmetinio-loginio duomenų konvertavimo įrenginio funkcijas. Kaip valdymo įrenginys, jis generuoja laikrodžio ir loginių signalų sekas, kurios nustato visų sistemos loginių įrenginių veikimo seką. Mikroprocesorius nustato ir nuosekliai atlieka programų komandų ištraukimo iš sistemos atminties, jų dekodavimo ir vykdymo mikrooperacijas. Mikroprocesoriaus veikimo tipas nustatomas pagal instrukcijose esantį operacijos kodą. Remdamasis šiais kodais, mikroprocesorius atlieka aritmetines, logines ar kitas operacijas su skaičiais, pateiktais dvejetainiu arba koduotu BCD.

Skaičiai, kurie atlieka operatyvines transformacijas aritmetiniame loginiame mikroprocesoriaus bloke, vadinami operandais. Operandas gali būti vienas iš pradinių skaičių, rezultatas, konstanta arba koks nors parametras. Operacija mikroprocesoriuje atliekama su vienu arba dviem operandais.

Mikroprocesorinės sistemos atmintis fiziškai įgyvendinama įvairių atmintinių pagrindu. Techninės ir ekonominės galimybės leidžia sukurti hierarchinę atmintį, pagrįstą puslaidininkiniais nuolatinės ir laisvosios prieigos atminties įrenginiais ir magnetiniais išoriniais atminties įrenginiais.

Fig.1 Loginė mikroprocesorinės sistemos struktūra

Puslaidininkiniai tik skaitymo atminties įrenginiai ROM leidžia tik nuskaityti iš anksto įrašytus duomenis sistemos veikimo metu. Jie pasižymi dideliu veikimo greičiu ir yra nepastovūs, t.y. išsaugoti informaciją, kai išjungiamas maitinimas.

Puslaidininkinės laisvosios kreipties atminties įrenginiai RAM veikia darbo (sutampančiais su mikroprocesoriaus tempu) duomenų rašymo ir skaitymo režimais. RAM trūkumas – jų nepastovumas, t.y. įrašytos informacijos praradimas, kai išjungiamas maitinimas.

Sistemos atmintis yra adresuojama, t.y. kiekvienas žodis įrašomas į atminties langelį su savo unikaliu adresu. Žodis yra dvejetainių vienetų (bitų) rinkinys – dvejetainiai skaitmenys, interpretuojami kaip atskiras skaičius arba kelios semantinės dvejetainių skaitmenų grupės. Norėdami gauti skaičių iš atminties arba įrašyti skaičių į atmintį, turite tiksliai nurodyti jo adresą atmintyje ir atlikti duomenų nuskaitymo iš atminties operaciją.

Duomenų įvesties įrenginiai (IDV) – bet kokios priemonės, skirtos duomenims iš išorės perkelti į mikroprocesorių registrus arba atmintį (valdymo pulto klaviatūra, įvestis iš perforuotųjų juostų ir perforuotų kortelių, išorinių saugojimo įrenginių magnetinėse juostose, kasetėse, diskuose, ekranuose ir kt.) .

Duomenų išvesties įrenginiai (UVvyv) – bet kokios priemonės, galinčios priimti duomenis, perduodamus iš mikroprocesorių registrų ar atminties elementų (ekranai, spausdinimo įrenginiai, išoriniai saugojimo įrenginiai, valdymo pultas ir kt.).

Norint sujungti įvairius duomenų įvesties ar išvesties įrenginius (taip pat ir kombinuotus įvesties-išvesties įrenginius), būtina visas jų jungtis ir signalus suvesti į standartinę formą, t.y. sąsajoms koordinuoti. Tam naudojamas specialus aparatūros blokas - IC informacijos valdiklis, kuris turi standartinę sąsają prisijungimo prie informacijos magistralės pusėje ir nestandartinę sąsają įvesties-išvesties įrenginių pusėje, t.y. kuri yra sąsajų sąsajų keitiklis.

Mikroprocesorius MP, RAM ir ROM kartu su UVvyv, skirtais operacijoms su asmeniu ar kita elektronine sistema, vadinamas mikrokompiuteriu. Mikrokompiuteris yra kompiuteris, kurio centrinė dalis, kaip procesoriaus, RAM, ROM ir informacijos valdiklio dalis, yra sukurta LSI pagrindu. Naudojant LSI kaip pagrindinius elementinius komponentus, mikrokompiuteriai turi tokius pranašumus, palyginti su kitų tipų kompiuteriais, kaip kompaktiškumas, patikimumas, mažos medžiagų sąnaudos, mažos energijos sąnaudos ir kaina. Tačiau mikrokompiuterio pagrindo struktūra ir mikroprocesoriaus greičio ribos lemia vidutines mikrokompiuterio veikimo charakteristikas. Tai reiškia mikrokompiuterius, kurių mikroprocesoriai yra vienoje ar daugiau lustų. Mikrokompiuteryje, paremtame dvipolių mikroprocesorių sekcijomis, galima pasiekti aukštą našumą, nes įdiegtas duomenų konvejerio apdorojimas ir didelės spartos labai efektyvus skaičiavimo proceso valdymas net ir turint pagrindinę struktūrą.

Mikrokompiuteris tampa centrine elektroninės valdymo, valdymo ir skaičiavimo sistemos dalimi, kai įvedamas į kokio nors objekto (proceso) valdymo kilpą. Norint susieti su mikrokompiuteriu, objektas (procesas) turi būti aprūpintas būsenos jutikliais ir pavaromis. Jutikliai veikia kaip informacijos įvesties į mikrokompiuterį šaltiniai, o pavaros veikia kaip išvesties informacijos imtuvai. Sąsajoms koordinuoti jutiklių ir pavarų prijungimas sistemoje atliekamas per jutiklių ir pavarų sąsajų blokus.

Atsižvelgiant į objekto (proceso) ypatybes ir mikroprocesoriaus galimybes, projektavimo etape nustatomas kiekvieno įrenginio ar bloko sudėtingumas. Sistemos dalys gali vystytis arba išsigimti, tačiau turi būti numatytas bendras visų elektroninių valdymo sistemų konstrukcijos ir veikimo principas. Dėl tiesioginio ryšio tarp programinės ir techninės įrangos funkcijų, kuriant elektroninę sistemą, galima sukurti arba techninę, arba sudėtingą programinę įrangą. Būtent šios aplinkybės lemia masines mikroprocesorinių valdymo sistemų panaudojimo galimybes beveik visose srityse.

Universalaus programuojamo valdiklio loginė struktūra.

Valdiklis (vietinis valdymo blokas) reikalingas informacijos įvesties-išvesties įrenginiams (ABV) valdyti. Ji užtikrina kompiuterio informacijos kanalo ir ABB dalių, kurios yra valdymo informacijos ir duomenų šaltiniai arba imtuvai, elektromechaninę ir loginę sąsają, nustato informacijos srauto tarp informacijos seką, kiekį, elektrinius parametrus, vietą laike ir kryptį. kanalus ir ABB. Pagrindinis valdiklio uždavinys – sudaryti sąlygas atrakinti ir užrakinti pavienius vožtuvus ar jų grupes, taip pat paleisti įvairaus tipo elektros variklius, elektromechaninius jungiklius, sužadinti solenoidus, priimti sustiprintus ir formuojamus įvairius signalus iš ABB informacinių jutiklių.

Naudojant bet kokias funkcinio sistemos padalijimo į dalis parinktis, sąsajos bloko su ABB aparatinė įranga yra arba integruota su mikroprocesoriaus LSI, arba atliekama atskirai sąsajos (sąsajos) LSI pavidalu.

Valdiklis gali būti įgyvendintas kaip standi jungtis tarp vartų grupių, šlepečių ir kt. kaip skaitmeninė mašina, pagrįsta aparatinės įrangos logika. Sumažinus integrinių grandynų paketų elektroninių komponentų skaičių, paprastai susidaro netvarkinga elektroninė struktūra, skirta tik konkrečiam naudojimui tam tikrame įrenginyje. Pakeitus laiko diagramą arba įvedus naujus signalus aparatūros valdiklyje, reikia perprojektuoti ir perprojektuoti visą valdiklį arba jo dalį.

Universalūs programuojami valdikliai realizuojami kaip vieno lusto LSI arba remiantis LSI mikroprocesorių rinkinių sekcijomis. Tokiuose valdikliuose įvairios signalų ir jų sekos laiko diagramos generuojamos ne paskirstant įprastus laikrodžio generatoriaus signalus laidinėmis jungtimis, o konvertuojant komandų sekas (mikroinstrukcijas). Dėl programinės įrangos ir programinės aparatinės įrangos lankstumo programuojamo valdiklio pritaikymas tam tikrai taikymo sričiai atliekamas perprogramuojant, o tai neturi įtakos valdiklio aparatinės įrangos diegimui arba sukelia tik valdymo atminties turinio perrašymą. įrenginiai.

Integrinių grandynų su dideliu elementų integravimo laipsniu techniniai ir ekonominiai parametrai leidžia valdyti kompiuterio ABB informaciją elektroninėmis struktūromis, panašiomis į valdymo kompiuterių struktūras. Tai suteikia: 1) funkcinį lankstumą naudojant pažangias komandų sistemas ir jomis pagrįstų įvairių sudėtingų signalų sekų konstravimą, atsižvelgiant į sistemos reakciją į išėjimo signalus; 2) paskirstytų valdymo metodų panaudojimas hierarchinėse valdymo sistemose, kai informacijos konvertavimo proceso optimizavimas vykdomas aukščiausiu valdymo lygmeniu, o tiesioginį vietinį valdymą vykdo integruotas valdiklis, kuris suvokia ir interpretuoja tiek ABB būsena ir aukštesnio valdymo lygio priemonių valdymo signalai; 3) ABB valdymo įrenginio specializacijos ir modifikavimo paprastumas.

Siųsti savo gerą darbą žinių bazėje yra paprasta. Naudokite žemiau esančią formą

Studentai, magistrantai, jaunieji mokslininkai, kurie naudojasi žinių baze savo studijose ir darbe, bus jums labai dėkingi.

Priglobta http://www.allbest.ru/

Ukrainos švietimo ir mokslo ministerija

Ukrainos nacionalinis technikos universitetas

"Kijevo politechnikos institutas"

Taikomosios matematikos katedra

Mikroprocesoriai ir mikroprocesorių sistemos

Atlikta:

Četverik Valerija Jaroslavovna

Grupė: KM-12

Patikrintas: Kopychko S.N.

- Įvadas

- 1. Mikroprocesorių raida

- 2.1 Asociatyvieji procesoriai

- 2.2 Matricos procesoriai

- 2.3 DNR procesoriai

- 2.4 Mobilieji procesoriai

- 2.6 Duomenų bazių procesoriai

- 2.7 Srautiniai procesoriai

- 2.9 Signalų procesoriai

- 3. Daugiaprocesorinės sistemos

- 3.4 Mikroprocesorinės sistemos su bendra atmintimi

- 3.5 Mikroprocesorinė sistema su vietine atmintimi

- 6. Individuali užduotis

- Literatūra

1. Mikroprocesorių raida

Procesorių istorija prasidėjo 1979 m., kai Intel išleido pirmąjį i4004 mikroprocesorių. Jis turėjo 4 bitų duomenų plotį, galimybę adresuoti 640 baitų atminties, 108 kHz taktinį dažnį ir 0,06 MIPS našumą. Toks procesorius jau galėtų veikti kaip skaičiuotuvo branduolys. Jame buvo 2300 tranzistorių ir jis buvo atliktas naudojant 10 mikronų skiriamosios gebos technologiją. Po metų pasirodė jo 8 bitų „giminaitis“ – i8008, adresuojantis jau 16 KB atminties.

1974 metais pasirodė 8 bitų i8080 procesorius ir tapo labai populiariu įrenginiu. Jis jau turėjo 2 MHz dažnį ir adresavo 64 KB atminties. 6000 tranzistorių leido pritaikyti 6 mikronų gamybos technologiją. Procesorius reikalavo trijų maitinimo šaltinių (+5V, +12V ir -5V) bei sudėtingo dviejų kontaktų sinchronizavimo. Šiame procesoriuje buvo pastatyti įvairūs terminalai, valdikliai ir net pirmasis „Altair“ kompiuteris. Mūsų šalyje pavėluotas 8086 aidas buvo 580IK80 ir KR580VM80 procesoriai, kurių pagrindu devintojo dešimtmečio pradžioje ir viduryje buvo sukurta daug „naminių“ kompiuterių.

Kitas žingsnis buvo i8085 procesorius (5 MHz, 0,37 MIPS, 6500 tranzistorių, 3 mikronų technologija). Jis išlaikė populiarią 8080 registro architektūrą ir programinės įrangos suderinamumą, tačiau pridėtas nuoseklusis sąsajos prievadas, pašalintos tam skirtos palaikymo IC (laikrodžio generatorius ir sistemos valdiklis) ir šiek tiek pakeista išorinė sąsaja. Pagrindinė dovana įrangos kūrėjams buvo viena maitinimo įtampa + 5V.

8080 ir 8085 temos variantas yra Z80 procesorius iš Zilog. Išlaikant programinės įrangos suderinamumą su 8080, į jį buvo įtraukti papildomi registrai, kurie leido žymiai pagerinti našumą. Rezultatas buvo įspūdingas – dar visai neseniai populiarūs Sinclair kompiuteriai, sukurti ant Z80, žaidimuose demonstruodavo grafiką, nenusileidžiančią kompiuteriams su 16 bitų 286 procesoriumi.

Pirmąjį 16 bitų 8086 procesorių „Intel“ išleido 1978 m. Dažnis – 5 MHz, našumas – 0,33 MIPS, tačiau instrukcijos jau su 16 bitų operandais (vėliau atsirado 8 ir 10 MHz procesoriai). 3 mikronų technologija, 29 tūkstančiai tranzistorių. Adresinė atmintis 1 MB. Registro architektūra ir instrukcijų sistema labai skyrėsi nuo 8080, tačiau bendrosios idėjos yra natūraliai atsekamos. Po metų pasirodė 8088 – tas pats procesorius, tik su 8 bitų duomenų magistrale. Tai pradėjo IBM asmeninio kompiuterio istoriją, kuri paliko pėdsaką tolesnei šios Intel procesorių linijos plėtrai. Masinis kompiuterių architektūros platinimas ir atvirumas sukėlė programinės įrangos laviną, kurią sukūrė didelės, vidutinės ir mažos įmonės bei pavieniai entuziastai. Techninis reikalavo (ir vis dar reikalauja) procesorių kūrimo, tačiau kompiuterinės programinės įrangos, kuri turi veikti naujesniuose procesoriuose, apkrova reikalavo ir atgalinio programinės įrangos suderinamumo. Taigi visos vėlesnių procesorių architektūros naujovės turėjo būti prijungtos prie esamo branduolio. Ir tada yra pati kompiuterio architektūra, „išmesta“, pavyzdžiui, pertraukimo vektoriaus naudojimo sudėtingumas. Pirmuosius 32 vektorius „Intel“ rezervavo „oficialiam naudojimui“, tačiau juos „perveikė“ kompiuterio BIOS pertraukimai. Vienas iš rezultatų yra papildomas būdas tvarkyti koprocesoriaus išimtis, naudojamas senesniuose kompiuteriuose.

80286 procesorius, pakeitęs kitą architektūros etapą, pasirodė tik 1982 m. Jame jau buvo 134 tūkstančiai tranzistorių (1,5 mikrono technologija) ir skirta iki 16 MB fizinės atminties. Jo esminė naujovė – apsaugotas režimas ir iki 1 GB talpos virtualioji atmintis – nerado masinio pritaikymo, procesorius dažniausiai buvo naudojamas kaip labai greitas 8088.

32 bitų procesorių klasė buvo atidaryta 1985 m. su 80386 modeliu (275 tūkst. tranzistorių, 1,5 mikrono). Duomenų magistralės (kaip ir vidinių registrų) plotis pasiekė 23 bitus, adresuojama fizinė atmintis – 4 GB. Atsirado nauji registrai, naujos 32 bitų operacijos, ženkliai patobulintas apsaugotas režimas, atsirado V86 režimas, atsirado ieškos atminties valdymas.

386 procesoriaus istorija primena 8086 istoriją: pirmasis modelis su 32 bitų duomenų magistrale (vėliau pavadintas 386DX) buvo pakeistas 386 SX su 16 bitų magistrale. Jis gana lengvai tilpo į PC AT architektūrą, kuri anksčiau buvo pagrįsta 286 procesoriumi.

„Intel486DX“ procesorius pasirodė 1989 m. Tranzistoriai – 1,2 mln., 1 mikrono technologija. Jis labai skiriasi nuo 386 pirminės talpyklos ir integruoto matematinio koprocesoriaus išdėstymu mikroschemoje (ankstesni procesoriai turėjo galimybę naudoti išorinius x87 koprocesorius). Be to, siekiant pagerinti našumą, šis CISC procesorius (taip pat ir vėlesni) naudoja RISC branduolį. Be to, atsirado jo atmainų, kurios skiriasi tuo, ar yra ar nėra koprocesoriaus, naudojamas vidinis dažnių dauginimas, talpyklos rašymo politika ir kt. Jie ėmėsi taupyti energiją (atsirado SMM režimas), o tai atsispindėjo ir 386 procesorių linijos tęsime (atsirado procesorius Intel386SL).

1993 metais pasirodė pirmieji Pentium procesoriai su 60 ir 66 MHz dažniu – 32 bitų procesoriai su 64 bitų duomenų magistrale. 3,1 milijono tranzistorių, 0,8 mikrono technologija, maitinimas 5 V. Jis iš esmės skiriasi nuo 486 savo superskaliarine architektūra – galimybe per vieną ciklą išleisti iki dviejų instrukcijų iš vamzdynų (o tai, žinoma, nereiškia instrukcijų perdavimo galimybės per procesorių per pusę ciklo arba vieną ciklą).

Pentium procesoriai, kurių dažnis 75, 90 ir 100 MHz, pasirodę 1994 m., pristatė antrosios kartos Pentium procesorius. Beveik tiek pat tranzistorių jie buvo pagaminti naudojant 0,6 mikrono technologiją, kuri leido sumažinti energijos suvartojimą. Jie skyrėsi nuo pirmosios kartos vidiniu dažnių dauginimu, kelių procesorių konfigūracijų palaikymu ir turėjo skirtingą korpuso tipą. Yra versijų (miniatiūriniame pakete 75 MHz), skirtų mobiliosioms programoms (nešiojamiesiems kompiuteriams). Antros kartos Pentium procesoriai tapo gana populiarūs asmeniniuose kompiuteriuose. 1995 metais pasirodė 120 ir 133 MHz procesoriai, jau pagaminti naudojant 0,35 mikrono technologiją (pirmieji 120 MHz procesoriai taip pat buvo pagaminti naudojant 0,6 mikrono technologiją). 1996-ieji vadinami „Pentium“ metais – atsirado 150, 166 ir 200 MHz procesoriai, o „Pentium“ tapo įprastu procesoriumi plataus pritaikymo kompiuteriams.

Lygiagrečiai su Pentium kūrėsi ir Pentium Pro procesorius, pasižymėjęs „dinaminio instrukcijų vykdymo“ naujovėmis. Be to, jo korpuse buvo įdėta antrinė talpykla, kurios tūris iš pradžių buvo 256 KB. Tačiau 16 bitų programose, taip pat Windows 95 aplinkoje, jo naudojimas nesuteikia jokių pranašumų. Procesorius turi 5,5 milijono branduolių tranzistorių ir 15,5 milijono tranzistorių 256 KB antrinei talpyklai. Pirmasis procesorius su 150 MHz dažniu pasirodė 1995 metų pradžioje (0,6 mikrono technologija), o jau metų pabaigoje pasirodė 166, 180, 200 MHz dažnio procesoriai (0,35 mikrono technologija), kuriuose talpykla pasiekė 512 KB.

1997 m. pradžioje pasirodė Pentium MMX procesoriai. MMX plėtinys numato lygiagretų operandų grupės apdorojimą su viena komanda. MMX technologija skirta paspartinti daugialypės terpės programų vykdymą, ypač operacijas su vaizdais ir signalų apdorojimu. Be MMX plėtinio, šie procesoriai, palyginti su įprastu Pentium, turi dvigubai didesnę pirminę talpyklą, o kai kuriuos architektūrinius elementus pasiskolino iš Pentium Pr, o tai padidina Pentium MMX procesoriaus našumą įprastose programose. Pentium MMX procesoriai turi 4,5 milijono tranzistorių ir yra pagaminti naudojant -.35 mikronų technologiją. 1997 m. birželio mėn. galimi 166, 200 ir 233 MHz procesoriai.

MMX technologija buvo sujungta su Pentium Pro architektūra – ir 1997 metų gegužę pasirodė Pentium II procesorius. Tai šiek tiek sumažinta „Pentium Pro“ branduolio versija su didesniu vidiniu laikrodžio dažniu, pridėjus MMX palaikymą. Sunkumai dėl antrinės talpyklos įdėjimo į vieną paketą su procesoriumi buvo įveikti paprastu būdu – ant nedidelės spausdintinės plokštės buvo patalpintas lustas su procesoriaus šerdimi ir statinių atminties lustų rinkinys bei papildomos grandinės, įgyvendinančios antrinę talpyklą. -kasetė. Visi kristalai yra padengti bendru specialiu dangteliu ir aušinami specialiu ventiliatoriumi. Pagrindiniai laikrodžio dažniai yra 233, 266 ir 300 MHz.

Nagrinėjamos šeimos procesoriuose, pradedant nuo 486-ojo, naudojama kombinuota architektūra - CISC procesorius turi RISC branduolį. mikroprocesoriaus informacijos duomenys

„Intel“ 80 x 86 šeima prasidėjo nuo 16 bitų 8086 procesoriaus. Visuose senesniuose procesorių modeliuose, įskaitant 32 bitų (386, 486, Pentium, Pentium Pro) ir 64 bitų MMX plėtinį, yra sistemos komandų poaibis ir paskesni modeliai, užtikrinantys suderinamumą su anksčiau parašyta programine įranga.

Atrodo, kad skirtumai tarp x86-64 architektūros ir IA-32 yra net mažesni nei skirtumai tarp IBM z/Architecture ir S/390. Pagrindiniai x86-64 pakeitimai, palyginti su dabartine IA-32 būsena, yra nedideli ir tam tikra prasme panašūs į tuos, kurie buvo įvesti pereinant nuo 16 bitų prie 32 bitų x86 architektūros.

Šios naujovės apima:

64 bitų virtualūs adresai (konkrečiame įgyvendinime galimas mažesnis bitų gylis);

· "plokščia" (plokščia) adresų erdvė su viena kodų, duomenų ir krūvos erdve;

· 64 bitų programų skaitiklis (RIP);

· adresavimo režimas, susijęs su programos skaitikliu;

· bendrosios paskirties registrų (sveiko skaičiaus) išplėtimas iki 64 bitų;

· pridėti 8 naujus bendrosios paskirties registrus (R8-R15);

· Pridėta dar 8 SSE registrai XMM8-XMM15, kurių talpa 128 (atitinka Intel siūlomą SSE2 plėtinį).

Ryžiai. 1. Bendrosios paskirties registrų išplėtimas

„Indikacijos“ papildomiems registrams ir duomenų dydžiams įvedamos kaip komandų priešdėlis. Pagrindinių x86-64 registrų rinkinys parodytas 1 pav. Registrai yra 64 bitų, išskyrus 32 bitų EFLAGS registrą, 128 bitų XMM registrus ir 80 bitų ST slankiojo kablelio registrus. x86-64 architektūra visų pirma apima IA-32 SSE2 plėtinius, pristatytus kartu su Pentium 4.

Registras A adresuojamas kaip AX 16 bitų operacijoms, EAX – 32 bitų operacijoms ir RAX – 64 bitų operacijoms. Atliekant 32 bitų operacijas, kuriose sveikųjų skaičių registras yra rezultatų registras, 32 bitų reikšmės užpildomos nuo nulių iki 64 bitų reikšmėmis. 8 ir 16 bitų operacijos sveikųjų skaičių registruose nepakeičia viršutinių bitų.

Norėdami dirbti su 64 bitų adresavimu, x86-64 pristatė ilgą režimą (vadinkime jį „išplėstuoju režimu“). Veikimo režimas nustatomas LMA (Long Mode Active) valdymo bitu, kuris nustatomas, jei mikroprocesorius pereina į išplėstinį režimą. Išplėstiniame režime segmentų registrai ES, DS, FS, GS, SS yra ignoruojami. CS registre (kodo segmento deskriptoriuje) yra bitai, nurodantys mikroprocesoriaus darbo režimus.

X86-64 išplėstinis režimas turi du „antrinius režimus“: 64 bitų režimą ir suderinamumo režimą. Suderinamumo režimas užtikrina dvejetainį suderinamumą su 16 bitų ir 32 bitų x86 režimais. Subrežimo pasirinkimas valdomas CS.L bitu. Jei nustatyta 0 (suderinamumo režimas), 64 bitų operacinė sistema, veikianti LMA režimu, gali paleisti senesnes 16 bitų ir 32 bitų x86 programas. CS.D bitas yra atsakingas už operando dydžio pasirinkimą.

Pagal numatytuosius nustatymus 64 bitų režimu (LMA bitų rinkinys, CS.L = 1, CS.D = 0) naudojami 64 bitų adresai ir 32 bitų operandai. Naudodami instrukcijų priešdėlius, galite pakeisti operando dydį (nustatyti jį į 64 arba 16 bitų), taip pat pakeisti adreso dydį (nustatyti jį į 32 bitus).

32 bitų programos gali naudoti pirmuosius 4 GB virtualios atminties.

Norint išsiaiškinti mikroprocesorių su x86-64 architektūra ypatybes, reikia išanalizuoti EAX/EBX/ECX/EDX registrus, kuriuose yra CPUID komandos vykdymo rezultatai (skambinant, kaip ir anksčiau, į EAX įdėkite 8000_0000h ). Jei 29-asis EAX bitas yra 1, mikroprocesorius veikia išplėstiniu režimu.

2. Netradicinių struktūrų mikroprocesoriai

2.1 Asociatyvieji procesoriai

Asociatyvusis procesorius yra specializuotas procesorius, įdiegtas asociatyviojo saugojimo įrenginio (AMU) pagrindu, kuriame, kaip žinote, informacija pasiekiama ne pagal operando adresą, o pagal išskirtines savybes, esančias pačiame operande. Asociatyvinis procesorius (AP) skiriasi nuo tradicinio naudojimo RAM dviem ypatybėmis: duomenų apdorojimo įrankių buvimu ir galimybe lygiagrečiai rašyti į visas ląsteles, kurioms buvo užfiksuota atitiktis su asociatyvine funkcija. Paskutinė AP savybė yra žinoma kaip daugiafunkcis įrašymas.

Žodžių operacijų atlikimo metodas leidžia apibrėžti keturias asociatyvių procesorių klases:

lygiagretus;

bitų seka;

nuoseklus žodis po žodžio;

orientuota į bloką.

Kelių bitų procesoriaus elementai naudojami kaip apdorojimo elementai lygiagrečiame asociatyviame procesoriuje. Kiekvienas PE veikia su savo asociatyvinės atminties moduliu ir ieškomis, taip pat aritmetiniu ir loginiu m bitų žodžių apdorojimu. Pagal turinį pasirinktų žodžių perkėlimas tarp AZU ir PE užtikrinamas perjungimo grandinėmis. Procesoriaus elementai vienu metu vykdo tą pačią komandą, gaunamą iš valdymo procesoriaus. Be to, galima keistis duomenimis tarp asociatyvinės atminties modulių ir pagrindinės atminties, o prieiga šiuo kanalu daroma kaip įprastoje atmintyje – pagal adresus.

Lyginant su kitų klasių asociatyviniais procesoriais, lygiagretūs AP pasižymi didžiausiu našumu, tačiau tai pasiekiama didelių techninės įrangos sąnaudų sąskaita.

2.2 Matricos procesoriai

Masyvo procesorius susideda iš daugybės panašių procesorių, kurie vykdo tą pačią instrukcijų seką skirtingiems duomenų rinkiniams. Pirmasis pasaulyje toks procesorius buvo ILLIAC IV (Ilinojaus universitetas). Jis schematiškai parodytas fig. 2.6. Pradinė idėja buvo sukurti mašiną, susidedančią iš keturių kvadrantų, kurių kiekviename būtų 8 x 8 procesoriaus/atminties blokų matrica. Kiekvienam kvadrantui buvo vienas valdymo blokas. Jis siuntė komandas, kurias vienu metu vykdė visi procesoriai, o kiekvienas procesorius naudojo savo duomenis iš savo atminties (duomenys buvo įkeliami inicijavimo metu).

Šis sprendimas, kuris gerokai skiriasi nuo standartinės von Neumann mašinos, kartais vadinamas SIMD (Single Instruction-stream Multiple Data-stream) architektūra. Dėl labai didelių sąnaudų buvo pastatytas tik vienas toks kvadrantas, tačiau jis galėjo atlikti 50 milijonų slankiojo kablelio operacijų per sekundę. Jei mašina būtų sukurta naudojant keturis kvadrantus, ji galėtų atlikti 1 milijardą slankiojo kablelio operacijų per sekundę, o tokios mašinos skaičiavimo galia būtų dvigubai didesnė nei viso pasaulio kompiuterių.

Ryžiai. 2. ILLIAC IV matricos procesorius

2.3 DNR procesoriai

DNR procesorius pasižymi savo struktūra ir instrukcijų rinkiniu. Procesoriaus struktūra yra DNR molekulės struktūra. O komandų rinkinys – tai biocheminių operacijų su molekulėmis sąrašas. Kompiuterinės DNR atminties principas pagrįstas nuosekliu keturių nukleotidų (pagrindinių DNR grandinės blokų) sujungimu. Trys nukleotidai, susijungę bet kokia seka, sudaro elementarią atminties ląstelę – kodoną, kurio visuma vėliau sudaro DNR grandinę. Pagrindinis DNR kompiuterių kūrimo sunkumas yra susijęs su selektyviomis vieno kodono reakcijomis (sąveika) DNR grandinėje. Yra eksperimentinė įranga, leidžianti dirbti su vienu iš 1020 kodonų arba DNR molekulių. Kita problema yra savaiminis DNR surinkimas, dėl kurio prarandama informacija. Ji įveikiama įvedant į ląstelę specialių inhibitorių – medžiagų, kurios užkerta kelią cheminei savaiminio kryžminimo reakcijai.

2 .4 Korinio ryšio procesoriai

Sąvoka „neurokompiuteris“ šiuo metu reiškia gana plačią skaičiuoklių klasę. Formaliai bet koks aparatinis neuroninio tinklo algoritmo įgyvendinimas gali būti laikomas neurokompiuteriu – nuo paprasto biologinio neurono modelio iki simbolių atpažinimo sistemos ar judančių taikinių. Neurokompiuteriai nėra kompiuteriai įprastine to žodžio prasme. Šiuo metu technologija dar nepasiekė tokio išsivystymo lygio, kad būtų galima kalbėti apie bendrosios paskirties neurokompiuterį (kuris irgi būtų dirbtinis intelektas).

2.5 Ryšio procesoriai

Ryšių procesoriai yra mikroschemos, kurios yra standžiųjų ASIC ir lanksčių bendrosios paskirties procesorių derinys.

Ryšio procesoriai yra programuojami, kaip ir mums žinomi asmeninio kompiuterio procesoriai, tačiau sukurti atsižvelgiant į tinklo užduotis, optimizuoti tinklo veikimui ir pagal juos gamintojai – tiek procesoriai, tiek įranga – rašo programinę įrangą konkrečioms programoms.

Ryšio procesorius turi savo atmintį ir turi didelės spartos išorinius kanalus, skirtus prisijungti prie kitų procesoriaus mazgų. Didelės spartos ryšio procesorius su RISC branduoliu leidžia valdyti duomenų mainus keliais nepriklausomais kanalais, palaiko beveik visus įprastus apsikeitimo protokolus, lanksčiai ir efektyviai paskirstyti ir apdoroti nuosekliuosius duomenų srautus laiko padalijimo kanalais.

2.6 Duomenų bazių procesoriai

Duomenų bazių procesoriai (mašinos) šiuo metu vadinami techninės ir programinės įrangos sistemomis, skirtomis atlikti visas arba kai kurias duomenų bazių valdymo sistemų (DBVS) funkcijas. Jei anksčiau duomenų bazių valdymo sistemos buvo skirtos daugiausia tekstinei ir skaitmeninei informacijai saugoti, tai dabar jos skirtos įvairiausiems duomenų formatams, įskaitant grafiką, garsą ir vaizdą. Duomenų bazių procesoriai atlieka valdymo ir paskirstymo funkcijas, suteikia nuotolinę prieigą prie informacijos per šliuzus ir daugina atnaujintus duomenis naudodami įvairius replikacijos mechanizmus.

Šiuolaikiniai duomenų bazių procesoriai turi užtikrinti natūralų duomenų bazėse sukauptos informacijos ryšį su internetinėmis transakcijų apdorojimo priemonėmis ir interneto programomis. Tai turėtų būti sistemos, suteikiančios vartotojams galimybę bet kuriuo metu pasiekti ir analizuoti įmonės duomenis, neatsižvelgiant į tai, kur šie duomenys yra.

Norint išspręsti tokias problemas, reikia žymiai padidinti tokių sistemų našumą. Tačiau tradicinis daugelio šiuolaikinių DBVS funkcijų programinės įrangos diegimas bendrosios paskirties kompiuteriuose sukelia sudėtingas ir neproduktyvias sistemas, kurių patikimumas nėra pakankamai didelis. Būtina ieškoti naujų architektūrinių ir techninių sprendimų. Šiuo metu šioje srityje atliekami intensyvūs tyrimai leido suprasti, kad kaip duomenų bazių procesorius reikia naudoti specializuotas lygiagrečias skaičiavimo sistemas. Tokių sistemų kūrimas yra susijęs su paralelizmo įgyvendinimu atliekant operacijų ir operacijų seką, taip pat su konvejeriniu srautiniu duomenų apdorojimu.

2.7 Srautiniai procesoriai

Srauto procesoriai vadinami procesoriais, kurie yra pagrįsti daugelio duomenų apdorojimo viena instrukcija principu. Pagal Flynn klasifikaciją jie priklauso SIMD (vieno instrukcijų srauto / kelių duomenų srauto) architektūrai. SIMD technologija leidžia atlikti tą pačią operaciją, pvz., atimti ir sudėti, su keliais skaičių rinkiniais vienu metu. Srauto procesorius pagerina bendrą našumą, o tai ypač svarbu dirbant su 3D grafika. Gali būti vienas srautinio perdavimo procesorius (Single-streaming processor – SSP) ir kelių gijų procesorius (Multi-Streaming Processor – MSP).

Ryškus srautinių procesorių atstovas yra „Intel“ procesorių šeima, pradedant „Pentium III“, pagrįsta „Streaming SIMD Extensions“ (SSE) technologija. SIMD klasės atstovais laikomos procesorių matricos: ILLIAC IV, ICL DAP, Goodyear Aerospace MPP, Connection Machine 1 ir kt. Tokiose sistemose vienas valdiklis valdo kelis procesoriaus elementus. Kiekvienas procesoriaus elementas gauna tą pačią komandą iš valdymo įrenginio kiekvienu fiksuotu laiko momentu ir vykdo ją savo vietiniais duomenimis.

2.8 Procesoriai su daugiafunkcine (neaiškia) logika

Procesorius su neaiškia logika (neaiškia logika) yra pagrįstas neaiškia matematika.

Neaiškia logika neišspręs tų problemų, kurių negalima išspręsti remiantis dvejetaine logika, tačiau daugeliu atvejų ji yra patogiau, produktyvesnė ir pigesnė. Jo pagrindu sukurti specializuoti techninės įrangos sprendimai (neaiškios skaičiuoklės) suteiks realių pranašumų. Jei kaskaduosime neaiškius skaičiuotuvus, gausime vieną iš neuroprocesoriaus arba neuroninio tinklo variantų. Daugeliu atvejų šios sąvokos tiesiog sujungiamos, o bendras terminas vadinamas „neurozine logika“.

2.9 Signalų procesoriai

DSP568xx šeima yra pagrįsta 16 bitų fiksuoto taško DSP56800 procesoriaus šerdimi. Šis branduolys skirtas efektyviai išspręsti valdymo ir skaitmeninio signalo apdorojimo problemas. Jo instrukcijų rinkinys suteikia skaitmeninį signalo apdorojimą, kuris veikia geriausiais bendrosios paskirties DSP, ir patenkina poreikį lengvai sukurti kompaktiškas valdymo programas.

DSP56800 branduolys yra programuojamas 16 bitų CMOS procesorius, skirtas realaus laiko skaitmeninių signalų apdorojimui ir skaičiavimo užduotims. DSP56800 branduolys (26 pav.) susideda iš keturių funkcinių vienetų: programos valdymo, adresų generavimo, aritmetinio-loginio duomenų apdorojimo, bitų apdorojimo. Siekiant padidinti našumą, operacijos įrenginiuose atliekamos lygiagrečiai. Kiekvienas įrenginys turi savo registrų rinkinį ir valdymo logiką ir yra organizuotas taip, kad galėtų veikti nepriklausomai ir kartu su kitais trimis. Vidinės adresų ir duomenų magistralės sujungia atmintį, funkcinius ir periferinius įrenginius (atminties srityje yra periferinių įrenginių registrai). Taigi branduolys vienu metu įgyvendina kelių veiksmų vykdymą: valdymo įrenginys parenka pirmąją komandą, adresų generatorius generuoja iki dviejų antrosios komandos adresų, o ALU atlieka trečiosios komandos dauginimą. Yra alternatyvi galimybė: trečioje instrukcijoje operaciją gali atlikti ne ALU, o bitų procesorius. Dujotiekio architektūra leidžia įgyvendinti lygiagretų mikroschemoje esančių įrenginių veikimą ir žymiai sutrumpinti programos vykdymo laiką.

3. Daugiaprocesorinės sistemos

3.1 Bendrieji reikalavimai mikroprocesorinei sistemai

Norint palyginti skirtingus kompiuterius tarpusavyje, dažniausiai naudojami standartiniai našumo matavimo metodai. Šios metodikos leidžia kūrėjams ir vartotojams naudoti testų balus sprendimams įvertinti, o galiausiai būtent našumas ir kaina suteikia vartotojui racionalų pagrindą apsispręsti, kurį kompiuterį pasirinkti.

Svarbiausia kompiuterinių sistemų savybė yra patikimumas. Patikimumo didinimas grindžiamas gedimų prevencijos principu, sumažinant gedimų ir gedimų dažnį naudojant elektronines grandines ir komponentus, turinčius aukštą ir itin aukštą integracijos laipsnį, mažinant trukdžių lygį, lengvesnius grandinių veikimo režimus, užtikrinti terminius jų veikimo režimus, taip pat tobulinti įrangos surinkimo būdus.

Mastelio keitimas – tai galimybė padidinti procesorių skaičių ir galią, RAM ir išorinės atminties kiekį bei kitus skaičiavimo sistemos išteklius. Mastelio keitimą turi užtikrinti kompiuterio architektūra ir dizainas, taip pat atitinkami programinės įrangos įrankiai.

Programinės įrangos suderinamumas ir perkeliamumas. Programinės įrangos suderinamumo sąvoką pirmą kartą plačiu mastu panaudojo sistemos IBM/360 kūrėjai. Pagrindinis uždavinys projektuojant visą šios sistemos modelių gamą buvo sukurti architektūrą, kuri vartotojo požiūriu būtų vienoda visiems sistemos modeliams, nepriklausomai nuo kiekvieno iš jų kainos ir našumo. Didžiulius šio metodo privalumus, leidžiančius išlaikyti esamą programinės įrangos atsilikimą pereinant prie naujų (dažniausiai produktyvesnių) modelių, greitai įvertino tiek kompiuterių gamintojai, tiek vartotojai, ir nuo to laiko beveik visi kompiuterinės įrangos tiekėjai tai padarė. šiuos principus. , tiekdamas suderinamų kompiuterių seriją. Tačiau reikia pažymėti, kad laikui bėgant net ir pati pažangiausia architektūra neišvengiamai pasensta ir atsiranda būtinybė kardinaliai keisti skaičiavimo sistemų architektūrą ir organizavimo būdus.

3.2 Lygiagrečių duomenų apdorojimo sistemų klasifikavimas

Yra keturi pagrindiniai lygiagretaus apdorojimo sistemų architektūros tipai:

Vamzdynų ir vektorių apdorojimas. Konvejerinio apdorojimo pagrindas yra atskiras tam tikros operacijos vykdymas keliais etapais (keliems etapams), perduodant duomenis iš vieno etapo į kitą. Tokiu atveju produktyvumas didėja dėl to, kad vienu metu skirtingose konvejerio stadijose atliekamos kelios operacijos.

Dujotiekio sudarymas yra efektyvus tik tada, kai dujotiekis yra beveik visiškai apkrautas, o naujų operandų padavimo greitis atitinka didžiausią dujotiekio pralaidumą. Jei atsiranda delsos, lygiagrečiai bus atliekama mažiau operacijų ir bendras našumas sumažės. Vektorinės operacijos suteikia idealią galimybę visiškai įkelti skaičiavimo dujotiekį.

SIMD tipo sistemos. SIMD tipo mašinos susideda iš daugybės identiškų procesoriaus elementų, turinčių savo atmintį. Visi procesoriaus elementai tokioje mašinoje vykdo tą pačią programą. Akivaizdu, kad tokia mašina, sudaryta iš daugybės procesorių, gali užtikrinti labai didelį našumą tik atliekant tas užduotis, kuriose visi procesoriai gali atlikti tą patį darbą. SIMD įrenginio skaičiavimo modelis yra labai panašus į vektorinio procesoriaus: su dideliu duomenų bloku atliekama viena operacija.

MIMD tipo sistemos. Terminas „daugiaprocesorius“ apima daugumą MIMD įrenginių ir (panašiai kaip terminas „matricinis procesorius“ taikomas SIMD įrenginiams) dažnai vartojamas kaip MIMD įrenginių sinonimas. Daugiaprocesorinėje sistemoje kiekvienas procesoriaus elementas (PE) vykdo savo programą visiškai nepriklausomai nuo kitų procesoriaus elementų.

Daugiaprocesorinės sistemos su SIMD procesoriais. Daugelis šiuolaikinių superkompiuterių yra kelių procesorių sistemos, kuriose kaip procesoriai naudojami vektoriniai procesoriai arba SIMD tipo procesoriai. Tokios sistemos priklauso MSIMD klasės mašinoms.

3.3 Ryšio modeliai ir atminties architektūros

Kiekvienas iš duomenų mainų mechanizmų turi savų privalumų. Jei norite bendrinti bendroje atmintyje, tai apima:

Suderinamumas su gerai suprantamais mechanizmais, naudojamais tiek vieno procesoriaus, tiek mažo masto kelių procesorių sistemose, kurios mainams naudoja bendrą atmintį

Lengvas programavimas, kai ryšio tarp procesorių modeliai yra sudėtingi arba dinamiškai keičiasi vykdymo metu. Tokie pranašumai palengvina kompiliatoriaus kūrimą.

Mažesnis keitimosi delsos laikas ir geresnis pralaidumo panaudojimas keičiantis nedidelėmis duomenų dalimis

Galimybė naudoti aparatūros valdomą talpyklą, kad būtų sumažintas nuotolinio ryšio dažnis, leidžiantis talpykloje saugoti visus duomenis, tiek bendrinamus, tiek nebendrinamus.

Pagrindiniai apsikeitimo naudojant pranešimų perdavimo pranašumai yra šie:

Techninė įranga gali būti paprastesnė, ypač lyginant su bendros atminties modeliu, kuris palaiko keičiamo dydžio talpyklos nuoseklumą.

Keitimosi modeliai yra suprantami, todėl programuotojai (arba kompiliatoriai) verčia atkreipti dėmesį į mainus, kurie paprastai turi didelių išlaidų.

Vertinant bet kokį mainų mechanizmą, svarbiausios yra trys veikimo charakteristikos:

1. Pralaidumas: Idealiu atveju mainų mechanizmo pralaidumą ribos procesoriaus, atminties ir sujungimo sistemos pralaidumas, o ne jokie mainų mechanizmo aspektai. Su mainų mechanizmu susijusios papildomos išlaidos (pavyzdžiui, tarpprocesoriaus ryšio trukmė) tiesiogiai veikia pralaidumą.

2. Vėlavimas: Idealiu atveju delsa turėtų būti kuo mažesnė. Norint jį nustatyti, labai svarbios yra techninės ir programinės įrangos, susijusios su mainų inicijavimu ir užbaigimu, pridėtinės išlaidos.

3. Slėpimo uždelsimas: kaip gerai mechanizmas paslepia vėlavimą, perdengdamas mainus su skaičiavimais ar su kitais mainais.

Kiekvienas iš šių veikimo parametrų turi įtakos mainų savybėms. Visų pirma, delsa ir pralaidumas gali skirtis priklausomai nuo elemento dydžio. Apskritai mechanizmas, kuris vienodai gerai veikia tiek su nedideliu, tiek su dideliu duomenų kiekiu, bus lankstesnis ir efektyvesnis.

3.4 Daugiaprocesorinės sistemos su bendra atmintimi

Raktas įgyvendinant tiek rašymo su atšaukimu, tiek rašymo su atnaujinimu schemą kelių procesorių sistemose su nedideliu procesorių skaičiumi yra magistralės mechanizmo naudojimas šioms operacijoms atlikti. Norėdami atlikti atnaujinimo arba atmetimo operaciją, procesorius tiesiog paima magistralę ir per ją paverčia adresą, kuriuo duomenys turėtų būti atnaujinti arba išmesti.

Visi procesoriai nuolat stebi magistralę, stebi joje pasirodančius adresus. Procesoriai patikrina, ar magistralėje pasirodęs adresas yra jų talpykloje. Jei taip, atitinkami duomenys talpykloje arba anuliuojami, arba atnaujinami, atsižvelgiant į naudojamą protokolą. Nuoseklios prieigos tvarka, būdinga magistralei, taip pat užtikrina, kad rašymo operacijos būtų griežtai nuoseklios, nes kai du procesoriai varžosi dėl rašymo į tą pačią vietą, vienas iš jų turi pasiekti magistralę anksčiau už kitą.

Stebėjimo procesui įgyvendinti gali būti naudojamos įprastos talpyklos žymos. Be to, anksčiau minėtas galiojantis bitas leidžia lengvai įgyvendinti atšaukimą. Skaitymo praleidimus, nesvarbu, ar priežastis buvo pripažinimas negaliojančiu, ar koks nors kitas įvykis, taip pat nesunku suprasti, nes jie tiesiog pagrįsti stebėjimo galimybe. Rašymo operacijoms taip pat norėtume sužinoti, ar yra kitų talpykloje esančių bloko kopijų, nes jei tokių kopijų nėra, rašymas negali būti siunčiamas į magistralę, todėl sutrumpėja rašymo užbaigimo laikas, taip pat reikiamo pralaidumo.

3.5 Daugiaprocesorinės sistemos su vietine atmintimi

Yra du skirtingi didelio masto paskirstytos (vietinės) atminties sistemų kūrimo būdai. Paprasčiausias būdas yra pašalinti aparatūros mechanizmus, užtikrinančius talpyklos nuoseklumą, ir sutelkti dėmesį į keičiamo dydžio atminties sistemos kūrimą.

Siekiant išspręsti nuoseklumo problemas, bendrinami (bendrinami) duomenys talpykloje nesaugomi. Žinoma, programinė įranga gali įdiegti tam tikrą bendrinamų duomenų talpyklos schemą, nukopijuodama juos iš bendros adresų erdvės į konkretaus mazgo vietinę atmintį. Tokiu atveju atminties nuoseklumą taip pat valdys programinė įranga. Šio metodo privalumas yra tas, kad reikalingas techninės įrangos palaikymas yra praktiškai minimalus, nors, pavyzdžiui, tokių funkcijų kaip blokinis (grupinis) duomenų kopijavimas būtų labai naudingas. Tokios organizacijos trūkumas yra tas, kad kompiliatoriaus programinės įrangos palaikymo mechanizmai, užtikrinantys tokio tipo talpyklos atmintį, yra labai riboti. Dabartinė technika daugiausia tinka programoms su gerai struktūrizuotu lygiagretumu programos ciklo lygmeniu.

4. Mikroprocesorinių sistemų mainų režimai

Pagrindiniai mainų režimai yra programinės įrangos valdomi mainai, pertraukimo režimo mainai ir tiesioginės atminties prieigos mainai.

Programos valdomas keitimasis vykdomas apdorotos komandos iniciatyva ir apima informacijos nuskaitymą į mikroprocesorių iš OP, informacijos įrašymą į OP iš MP, informacijos įvedimą į MP iš TPB ir informacijos išvedimą iš MP į MP. VU. Apsvarstykite išvardytus mainų tipus.

Informacijos skaitymas į mikroprocesorių iš pagrindinės atminties pradedamas nuo to momento, kai išduodama OP ląstelės adreso reikšmė, iš kurios reikia nuskaityti informaciją iš MP į SHA. Pagal sinchronizuojantį impulsų „skaitymą“ (RD), ateinantį iš MP į SHU, aktyvuojami norimi OP langeliai. Informacija iš OP patenka į SD, perkeliama į MP ir įrašoma į atitinkamą MP registrą.

Informacijos rašymas į pagrindinę atmintį iš MP prasideda taip pat, kaip ir pirmuoju atveju: nuo MP į SHA gaunama OP langelio, į kurį turi būti daromas įrašas, adreso reikšmė ir MP sugeneruoja. „rašymo“ signalas (WR) SHU linijoje. Tuo pačiu metu informacija iš MP patenka į SD, perkeliama į OP ir įrašoma į atitinkamą atminties langelį.

Informacijos įvedimas į MP iš išorinio įrenginio prasideda sinchronizacijos signalu iš valdymo įrenginio arba MP, bet konkretaus KVV kanalo, kuris yra prijungtas prie reikiamo TPB ir per kurį įvedama (nuskaitoma) informacija į MP bus siunčiamas į SHA. Toks kanalas vadinamas prievadu. Po kurio laiko linija SHU MP generuoja valdymo signalą RD "skaitymas" (arba "įvestis"). Prievadas, kurio prašoma nurodytu adresu, aktyvuojamas, o gavus RD signalą, informacija iš TPB per prievadą patenka į žingsninį variklį. Pagal ją informacija perduodama MP.

Informacijos išvedimas iš MP į išorinį įrenginį vykdomas MP formuojant KVV kanalo (prievado), prijungto prie reikiamo TPB, adreso eilutėse SHA. Po tam tikro laiko MP generuoja WR „įrašo“ (arba „išvesties“) signalą WR linijoje ir išveda į SD informaciją, kurią reikia įrašyti (išvesti) į reikiamą TPB. Išvesties prievadas, kurio prašoma nurodytu adresu, aktyvuojamas ir informacija iš SD patenka į nurodytą TPB.

Nutraukti mainus. Keitimasis pertraukimo režimu yra skirtas apdoroti TPB sugeneruotas pertraukimo užklausų paslaugų programas, joms kaupiant informaciją veikimo metu. TPB generuojamų pertraukimo užklausų laikas yra atsitiktinis reiškinys ir daugeliu atvejų negali būti užprogramuotas.

Keitimąsi pertraukimo režimu inicijuoja šį TPB aptarnaujantis TPB arba KVV ir yra vykdomas būtent tais momentais, kai atitinkamas TPB yra paruoštas duomenų perdavimui į MP. Kai tik yra pasiruošęs perduoti duomenis, šį TPB aptarnaujantis pertraukimų valdiklis generuoja pertraukimo užklausos signalą, kurį MP analizuoja ir, jei reikia, pertraukia apdorojamą programą ir pereina prie mainų operacijos – pertraukimo paslaugos įvedimo ir apdorojimo. programa.

Yra techninė, programinė įranga ir specialūs pertraukimai.

Aparatinės įrangos pertraukimai, praktikoje dar vadinami išoriniais pertraukimais, įvyksta veikiant TPB generuojamiems signalams, kuriems reikalinga priežiūra. Aparatinės įrangos pertraukimai, kaip taisyklė, naudojami TPB aptarnavimui šių įrenginių prašymu. Jie gali būti nemaskuojami ir maskuojami.

Neužmaskuojami pertraukimai yra pertraukimai, kuriuos sukelia išorinė aparatinė įranga ir kurių vykdoma programa negali išjungti. Tokių pertraukimų užklausos siunčiamos į specialų mikroprocesoriaus įvestį – nemaskuojamų pertraukimų įvestį. Jie aptarnaujami be klaidų ir nedelsiant, nepaisant šiuo metu vykdomos programos svarbos.

Užmaskuojami pertraukimai – pertraukimai, kuriuos gali įjungti arba išjungti programinė įranga – įtraukiant į programą specialias instrukcijas, kurios įjungia arba išjungia pertraukimus tam tikroje programos dalyje. Norint įgyvendinti tokius pertraukimus, mikroprocesorius turi vieną ar daugiau užmaskuojamų pertraukimo paslaugų užklausų įvesčių.

Keitimasis tiesioginės atminties prieigos režimu. Anksčiau aptartais režimais informacija keičiamasi tarp MP ir OP arba tarp MP ir TPB. Tačiau praktikoje dažnai reikia greitai keistis informacija tarp TPB ir OP jos neapdorojus. Šiuo atveju, naudojant anksčiau aprašytus režimus, keitimo procedūrą turi sudaryti du ciklai. Pirmuoju ciklu informacija pirmiausia turi būti perkelta iš TPB (arba OP) į MP akumuliatorių, antrajame cikle informacija iš akumuliatoriaus turi būti įvedama į OP (arba TPB).

Keičiantis su lėtai veikiančiais TPB ir perduodant didelius informacijos kiekius, tokia dviejų etapų procedūra žymiai sumažina valiutos kursą, tai yra, sumažėja visos MPS našumas. Šiuo atžvilgiu naudojamas mainų metodas, kai informacija įrašoma į OP iš TPB arba informacija nuskaitoma iš atminties į išorinį įrenginį tiesiogiai, nedalyvaujant MP. Šis mainų tipas vadinamas tiesioginės atminties prieigos (DMA) mainais.

Keitimuisi organizuoti naudojamas specialus valdymo įrenginys - PDP valdiklis, kuris keitimosi metu atlieka aktyvaus įrenginio funkcijas, tai yra nustato mainuose dalyvaujančio TP celės arba TPB prievado adresą. SHA linijose, generuoja reikiamus valdymo signalus SHU linijose, nustato informacijos perdavimo per SD linijas pradžią.

Programiniu būdu valdomo mainų ir pertraukimo režimo keitimo atveju MP valdo magistralę (adreso, duomenų ir valdymo magistrales). Keičiant DMA režimu, magistralė turi būti perduota DMA valdiklio žinion, o MP turi būti atjungtas nuo magistralių. Šiuo tikslu MP suteikia specialaus valdymo signalo „padangos gaudymo užklausos“ įvestį, kurį gavęs, pasibaigus einamajam komandos vykdymo ciklui, MP valdymo įtaisas perjungia savo padangų buferinius įrenginius į režimą su didelė išėjimo varža (didelės varžos būsena). Tuo pačiu metu MP atjungiamas nuo magistralinių kamienų, o jo valdymo įtaisas specialia valdymo linija generuoja magistralės gaudymo leidimo signalą PDP valdikliui ir perduoda magistralę, kad būtų galima perduoti vieną žodį arba visą informacijos masyvą. .

5. Informacijos perdavimo kanalai mikroprocesorinėse sistemose

Sąsajos grandinės skirstomos į kelis lygius:

1 lygio magistralės sąsajos užtikrina informacijos mainus tarp visų (arba pagrindinių) mikroprocesorinės sistemos modulių. Daugumos tokio lygio magistralių pasirinkimą lemia mikroprocesoriaus architektūra, pavyzdžiui, I-41 (Multibus) sąsaja naudojama K580, K1810 serijos MPC, intermodulinė lygiagreti sąsaja (IPI) - K1801/ 1809, K1811, K581, K5S8 serijos MPC ir kt.

S-100 magistralė buvo sukurta 8 bitų mikroprocesoriams ir įvairioms pramonės reikmėms.

Jo tipinės savybės buvo šios:

Matmenys: 134 mm x 254 mm, 100 kaiščių

Jungtis: 50 kontaktų kiekvienoje plokštės pusėje

Nereguliuojama maitinimo įtampa: +8V, +16V.

ISA magistralė. PC AT kompiuteriuose, kuriuose naudojamas i80286 mikroprocesorius, pirmą kartą pradėta naudoti nauja ISA (Industry Standard Architecture) sistemos magistralė, visiškai realizuojant minėto mikroprocesoriaus galimybes. Adreso eilučių skaičius padidintas keturiomis, o duomenų eilučių skaičius – aštuoniomis. Taigi buvo galima lygiagrečiai perkelti 16 bitų duomenų ir 24 adresų eilučių dėka tiesiogiai pasiekti 16 MB sistemos atminties. Aparatinės įrangos pertraukimo linijų skaičius šioje magistralėje padidintas nuo 7 iki 15, o DMA kanalų skaičius nuo 4 iki 7.

EISA magistralė suteikia didesnį galimą adresuojamos atminties kiekį, 32 bitų duomenų perdavimą, įskaitant DMA režimą, patobulintą pertraukimo sistemą ir DMA arbitražą, automatinį sistemos konfigūravimą ir išplėtimo korteles.

„Nubus“ magistralė turi maždaug tokias pačias charakteristikas kaip ir „ISA“.

„Multibus-II“ magistralė buvo sukurta 1985 m. kaip „Multibus“ standarto, plačiai naudojamo pramoninėje automatizacijoje, plėtra. Multibus-II yra 32 bitų magistralė ir gali veikti valdymo procesoriaus greičiu – iki 80 MB/s. Skirtingai nuo kitų čia aptartų magistralių, „Multibus“ turi galimybę greitai perduoti pranešimus tarp skirtingų valdymo įrenginių. Tuo pačiu metu perdavimo mechanizmas leidžia organizuoti „protingą“ procesorių ir valdiklių sąveiką. Tai ypač svarbu kuriant kelių procesorių sistemas ir kuriant sudėtingus pramoninės elektronikos kompleksus.

MC magistralė (MicroChannel) pasirodė 1987 m. PS/2 kompiuteriuose. Pakankamai greita (iki 20 MHz, iki 76 MB/s) ir plati (32 bitai) magistralė turėjo nemažai sėkmingų architektūrinių sprendimų ir galėjo lengvai konkuruoti dėl lyderystės tarp sisteminių magistralių.

Jis turi šias funkcijas:

8/16/32 – bitų duomenų linijos,

Pertraukimai pagal signalo lygį (skirtingai nei ISA, kur pertraukimai yra prie laikrodžio signalo krašto),

24 arba 32 adresų eilutės (adresuojamos iki 4 GB atminties),

Automatinė plokščių konfigūracija (remiantis šių plokščių ROM informacija),

Asinchroninis duomenų perdavimo protokolas.

Sbus buvo sukurtas 1989 m., kad galėtų veikti iki 25 MHz. Jis skirtas 32 bitų duomenų perdavimui. Jo ypatybė – galimybė automatiškai išversti virtualius adresus į fizinius, atpažinti duomenų perdavimo klaidas ir inicijuoti pakartotinius bandymus.

Mbus buvo sukurtas 1990 m. ir skirtas 64 bitų duomenims perduoti. Mbus yra suderinamas su kitais autobusais, turi nešiojamas parinktis ir apima pranešimų siuntimo galimybes.

SCSI magistralę (Small Computer System Interface) reguliuoja IEC 9316 standartas, kuris suvienija pagrindinius pagrindinių tipų periferinių įrenginių, daugiausia magnetinių diskų įrenginius, ADC, lygius, taip pat galimybę išplėsti funkcijas naudojant specialius kodus ir laukus. . Sąsaja naudoja loginį visų duomenų blokų adresavimą ir galimybę nuskaityti informaciją apie galimų blokų skaičių iš tiesioginės prieigos įrenginių.

PCI magistralė turi keletą pranašumų, palyginti su pagrindine VL-Bus. Prie magistralės pagal PCI specifikaciją galima prijungti iki 10 įrenginių. Tačiau tai nereiškia, kad reikia naudoti tą patį išplėtimo lizdų skaičių – apribojimas taikomas bendram komponentų skaičiui, įskaitant tuos, kurie yra pagrindinėje plokštėje. Kadangi kiekvieną PCI išplėtimo plokštę galima dalytis dviem išoriniais įrenginiais, bendras įdiegtų lizdų skaičius sumažėja.

MPI sąsaja su multipleksuotomis adresų ir duomenų linijomis yra sukurta siekiant užtikrinti informacinį ir elektrinį sistemos įrenginių suderinamumą. Jis įgyvendinamas remiantis stuburu ir loginiais mazgais, esančiais kiekviename prie jo prijungtame įrenginyje. Įrenginiai kartu sudaro vieną pagrindinio tinklo adresų erdvę.

„Unibus“ sąsajoje yra 56 signalų linijų pagrindas. Visi įrenginiai yra prijungti prie šių linijų lygiagrečiai. Prioritetinei magistralei valdyti naudojamos penkios vienakryptės signalo linijos, likusios 51 linija yra dvipusės; 18 adresų eilučių naudoja pagrindinis valdiklis, kad pasirinktų, su kuriuo pavaldiniu bendrauti. Viena iš adreso eilučių nurodo baitą, kurį reikia pasiekti atliekant operacijas su baitais; 16 duomenų linijų naudojama informacijai perduoti tarp pagrindinio ir pavaldinio. Dvi valdymo linijos apibrėžia vieną iš keturių galimų mainų operacijų (du įvesties režimai ir du išvesties režimai).

I-41 sąsaja yra vienas iš Multibus sąsajos variantų, jungiantis standartizuotas sąsajas IEEE, VME – magistralę, AMS – magistralę ir kt., išlaikant linijų sudėtį ir jų funkcijas.

2 lygmens sąsajos suteikia išorinių įrenginių ir komunikacijos įrenginių su objektais (USO) derinį, kuris naudojamas tais atvejais, kai TPB ir OCO neturi įmontuotos sistemos sąsajos ir negali būti tiesiogiai prijungtos prie sistemos magistralės. Čia plačiausiai naudojama IRPS sąsaja, skirta įrenginių su nuosekliuoju informacijos perdavimu radialiniam prijungimui, ir IRPR sąsaja įrenginių su lygiagrečiu informacijos perdavimu prijungimui. Jų pagalba sujungiami beveik visi išoriniai įrenginiai (ekranai, spausdintuvai, klaviatūros, braižytuvai ir kt.), išskyrus išorinius saugojimo įrenginius, kurie kelia didesnius reikalavimus sąsajos pralaidumui.

3 sluoksnio sąsajos skirtos jutikliams ir pavaroms sujungti. Dėl daugybės jutiklių ir pavarų iki šiol buvo sukurta daugybė šių sąsajų. Sąsajos

4 lygiai yra duomenų perdavimo įrenginių (DDU) sąsajos. Tai apima telegrafo, telefono, aukšto dažnio, šviesolaidinio ir kitų kanalų sąsajas, skirtas duomenų perdavimui dideliais atstumais. Tai taip pat apima bendrosios ir specialiosios paskirties paskirstytų valdymo sistemų sąsajas (KAMAK IEC - 640, IEC - 625 - 1 nuoseklusis, ILPS - 2 ir kt.) ir bendrosios paskirties vietinių tinklų sąsajas (R - 802 ir kt.)

5 sluoksnio sąsajos apima sąsajas, kurios yra išorinės mikroprocesorinės sistemos. Išorinė sąsaja yra prijungta prie sistemos sąsajos naudojant specialų sąsajos adapterį.

AGP sąsaja sukurta informacijai perduoti į išorinius įrenginius, įskaitant duomenų rodymą. Jame yra magistralė ir informacijos perdavimo įrenginys (vaizdo greitintuvas), kurie sudaro sąsajos grandinę. Šiuo metu AGP sąsaja yra plačiausiai naudojama.

6. Individuali užduotis

Intel Pentium T2130

„Intel Pentium T2130“ yra dviejų branduolių mikroprocesorius, naujausias „Dual-Core T2xx“ linijos narys, išleistas 2007 m. balandžio mėn.

Ypatumai:

2 srautai

Patobulinta SpeedStep technologija

Vykdykite išjungimo bitą

Palaikykite MMX, SSE, SSE2, SSE3

„Intel®“ virtualizacijos technologija (VT-x)

Procesoriaus lizdas - lizdas M

Architektūra:

„Intel Pentium Dual-Core T2130“, pagrįsta patobulintu Pentium M.

151 milijonas tranzistorių

Procesoriaus šerdies dydis – 90mm?

Procesoriaus branduolys – Yonah

Charakteristikos:

Mikroprocesorius Intel Pentium Dual-Core T2130 turi 2 branduolius, kurių dažnis yra 1,86 GHz.

Sistemos magistralės dažnis – 533 MHz

1 lygio talpykla – 2 x 32 KB instrukcijos 2 x 32 KB duomenų talpyklos

2 lygio talpykla – 1 MB

Didžiausia galia 31 W.

Darbinė įtampa 1 - 1,3 V

Privalumai:

Jis turi palyginti mažą kainą.

Patobulinta Intel SpeedStep technologija.

Užtikrina aukštą kompiuterių našumą.

Mažas energijos suvartojimas

daugiafunkcinis darbas

Trūkumai:

Ribotas talpyklos dydis.

Nepalaiko ECC atminties (aparatinės įrangos klaidų taisymo atminties).

Nepalaiko Turbo Boost, Hyper Threading technologijų

Nepalaiko 64 bitų skaičiavimo

Literatūra

1. http://www.osp.ru/os/2002/04/181300/

2. https://ru.wikipedia.org/wiki/X86-64

3. http://www.nsc.ru/win/elbib/data/show_page.dhtml?77+852

4. http://www.island-formoza.ru/arhitektura-pc/parallelizm-na-urovne-processorov.html

5. http://libeldoc.bsuir.by/bitstream/123456789/989/81.pdf

6. http://mrmarker.ru/p/page.php?id=14738

Priglobta Allbest.ru

...Panašūs dokumentai

Duomenų bazių teorijos (DB) apibrėžimai. Informacinių sistemų taikymo elementai. Reliacinių duomenų modeliai. Paskirstytų duomenų bazių valdymo sistemų užduotis. Paralelinio užklausų apdorojimo priemonės. Duomenų bazės naudojimas inventoriui.

Kursinis darbas, pridėtas 2015-05-01

Duomenų perdavimo sistemų samprata ir klasifikacija. Belaidžio duomenų perdavimo sistemų charakteristikos. Laidinių duomenų perdavimo sistemų ypatybės: šviesolaidinės ir šviesolaidinės koaksialinės sistemos, vytos poros, laidai. Įrangos gamintojų vertinimas.

Kursinis darbas, pridėtas 2010-03-04

Bendra mikroprocesoriaus struktūra. 64 bitų atminties posistemio struktūra. I/O prievado pasirinkimas. Mikroprocesorinių sistemų sąsajos ypatybės. Atminties posistemio projektavimas Itanium 2 pagrindu. Informacijos turinio ir reikalingų tūrių skaičiavimas.

Kursinis darbas, pridėtas 2012-12-05

Mikroprocesorius kaip universalus įrenginys, skirtas atlikti programinį informacijos apdorojimą. Funkcionalumas ir architektūriniai sprendimai. Mikrovaldikliai valdymo ir informacijos apdorojimo sistemose. Elektroninių kompiuterių klasifikacija.

Kursinis darbas, pridėtas 2015-10-12

Skaičiavimo sistemų architektūrų klasifikacijos. Kompiuterinių sistemų organizavimas. CPU įrenginys. Šiuolaikinių kompiuterių kūrimo principai. Mikroprocesorinių sistemų evoliucija. Funkcinių vienetų skaičiaus ir sudėties padidėjimas.

baigiamasis darbas, pridėtas 2009-01-29

Šiuolaikinės duomenų apdorojimo sistemos. Automatizuota informacinė sistema. Informacijos samprata ir dinaminis modelis. Atsiranda daugybė skirtingų tipų sistemų, kurios skiriasi konstravimo principais ir jose įtvirtintomis informacijos apdorojimo taisyklėmis.

pristatymas, pridėtas 2013-10-14

Pagrindiniai kompiuterinės sistemos komponentai. Kūrimo istorija, mikroprocesorių naudojimo ypatumai. D-trigerio įtaisas ir veikimas. Scheminė diagrama, direktyvos, operatoriai ir programos aprašymas mikroprocesoriams, derintuvų tipai.

mokymo vadovas, pridėtas 2011-11-27

Ekonominės informacijos apdorojimo sistemų reikalavimai ir struktūra. Informacijos apdorojimo technologijų ir sistemų priežiūra, informacijos apsauga. Užklausų, formų, ataskaitų, makrokomandų ir modulių kūrimo procesas. Įrankiai duomenų bazių tvarkymui ir darbui su jomis.

Kursinis darbas, pridėtas 2012-04-25

Istorinė skaičiavimo įrenginių raida. Skaičiavimo sistemų blokinės schemos. Elementų bazės kūrimas ir pačių sistemų architektūros kūrimas. Pagrindinės kompiuterių klasės. Duomenų kanalai. Reikalavimai išorinių įrenginių sudėčiai.

santrauka, pridėta 2011-09-01

Pateiktos informacijos formos. Pagrindiniai naudojamo duomenų modelio tipai. Informacinių procesų lygiai. Informacijos paieška ir duomenų paieška. Tinklo saugykla. Duomenų saugyklų kūrimo ir priežiūros problemos. Duomenų apdorojimo technologijos.

Sąsaja yra programinės ir techninės įrangos rinkinys, skirtas informacijai perduoti tarp kompiuterio komponentų ir apima elektronines grandines, linijas, magistrales ir adresų signalus, duomenis ir valdymą, signalų perdavimo algoritmus ir signalų interpretavimo pagal prietaisus taisykles.

Plačiąja prasme sąsaja taip pat apima mechaninę dalį (suderinamumas naudojant standartines jungtis) ir pagalbines grandines, kurios užtikrina įrenginių elektrinį suderinamumą loginio signalo lygių, įvesties ir išėjimo srovių ir kt.

Išsamus sąsajų ir sistemos magistralių tyrimas nepatenka į šio kurso taikymo sritį. Todėl šiuos klausimus svarstysime tik bendros darbo organizavimo idėjos požiūriu. mikroprocesorinė sistema ir jį sudarančių prietaisų sąveikos principus.

Pagrindinis būdas organizuoti MPS yra magistralinis modulinis (8.1 pav.): visi įrenginiai, įskaitant mikroprocesorių, yra vaizduojami kaip moduliai, kurie yra tarpusavyje sujungti bendra magistrale. Keitimasis informacija ant bagažinės atitinka kai kurios bendros sąsajos, nustatytos šio tipo magistralėms, reikalavimus. Kiekvienas modulis yra prijungtas prie magistralės per specialias sąsajos grandines.

Ryžiai. 8.1.

Modulių sąsajų grandinėms priskiriamos šios užduotys:

- signalų funkcinio ir elektrinio suderinamumo užtikrinimas ir apsikeitimo protokolais moduliai ir sistemos greitkelis;

- modulio vidinio duomenų formato konvertavimas į sistemos magistralės duomenų formatą ir atvirkščiai;

- užtikrinant vieningų informacijos mainų komandų suvokimą ir jų pavertimą vidinių valdymo signalų seka.

Šios sąsajos grandinės gali būti gana sudėtingos. Paprastai jie įgyvendinami specializuoto mikroprocesoriaus LSI forma. Tokios schemos vadinamos valdikliai.

Valdikliai turi didelį savarankiškumo laipsnį, kuris leidžia lygiagrečiai veikti laiku periferiniai įrenginiai ir duomenų apdorojimo programos vykdymą mikroprocesoriumi.

Be to, iš anksto sutalpindami duomenis, valdikliai vienu metu perduoda daug žodžių, esančių nuosekliais adresais, o tai leidžia naudoti vadinamąjį „sprogstantįjį“.

( Burst ) magistralės režimas – 1 adreso ciklas, po kurio seka keli duomenų ciklai.

Magistralinio modulinio kompiuterio organizavimo būdo trūkumas yra tai, kad neįmanoma vienu metu sąveikauti daugiau nei dviem moduliams, o tai riboja spektaklis kompiuteris.

Mikroprocesoriaus sąveika su laisvosios kreipties atmintimi (RAM) ir išoriniais įrenginiais (TPB) pavaizduota fig. 8.2.

Ryžiai. 8.2.

Mikroprocesorius generuoja išorinio įrenginio arba RAM elemento adresą ir generuoja valdymo signalus – arba IOR / IOW kai pasiekiamas skaitymui / rašymui iš išorinio įrenginio, arba MR / MW skaitymui / rašymui iš RAM.

Yra tik 2 komandos, skirtos keistis informacija su išoriniais įrenginiais MP:

- įvesties komanda IN AX , DX įrašo į AX registrą numerį iš išorinio įrenginio, kurio adresas yra DX registre; tuo pačiu metu generuojamas IOR signalas (INput / OUTput Read ).);

- išvesties komanda OUT DX , AX išveda informaciją iš AX registro į išorinį įrenginį, kurio adresas yra DX registre; tai generuoja signalą IOW (INput / OUTput Write).

IOR/IOW signalai generuojami, kai vykdomos tik šios komandos.

MR / MW signalai formuojami komandose, kurių operandas ir (arba) rezultatų imtuvas yra RAM, pavyzdžiui, ADD , AX .

Šiuo atžvilgiu yra du pagrindiniai adresų erdvės organizavimo būdai mikroprocesorinė sistema:

- Su bendra adresų erdvė išoriniai įrenginiai ir RAM;

- su nepriklausomomis adresų erdvėmis.

Pirmuoju atveju įvesties / išvesties prievadus galima pasiekti kaip RAM langelius. Šio metodo pranašumas yra galimybė naudoti skirtingus adresavimo režimus, kai pasiekiate išorinius įrenginius, taip pat atlikti įvairias aritmetines ir logines operacijas su I / O prievadų turiniu. Tačiau tuo pat metu tai sumažina adresuotos RAM talpą ir sumažina sistemos saugumą, nes prarandama papildoma apsauga, susijusi su I / O komandų vykdymu (vėliavos registro IOPL laukas neveikia). Be to, programos logikos pažeidimas (neteisingo RAM adreso susidarymas) gali sukelti klaidingą išorinio įrenginio veikimą.

Jei pirmasis trūkumas nėra toks reikšmingas su šiuolaikiniais tūriais saugojimo įrenginiai, tada antrasis gali turėti labai neigiamos įtakos MPS darbui. Galimybė naudoti sudėtingus adresavimo režimus pasiekiant išorinius mikroprocesorių sistemų įrenginius, pagrįstus universaliais MP, nėra tokia svarbi. Todėl šiuo metu kuriant MPS pirmenybė teikiama antrajam požiūriui.

Apsvarstykite informacijos mainų tarp mikroprocesoriaus ir išorinių įrenginių ypatybes. Supaprastinta šio proceso laiko diagrama parodyta